### SCHOOL OF AERONAUTICS (NEEMRANA)

**FACULTY NAME: RAVIRAJ SRIKRISHNA**

**B.Tech AERONAUTICAL**

**SUBJECT CODE: EE101**

**SEMESTER: II**

**SUBJECT NAME: BASIC ELECTRICAL & ELECTRONICS**

## **UNIT - 1**

..

# CHAPTER - 1 BASIC CONCEPTS OF ELECTRICAL ENGINEERING

#### NATURE OF ELECTRICITY

According to Modern electron theory of matter, all matter whether solid, liquid or gas is composed of very small particles called molecules. A molecule is in turn made up of atoms. An **atom** consists of a central part called nucleus and around the nucleus (called extra-nucleus), there are a number of **electrons** revolving in different paths or orbits. The size of the nucleus is very small as compared to the size of the atom. The nucleus contains **protons** and **neutrons**. A proton is a positively charged particle having mass 1837 times that of an electron. A neutron has the same mass as proton but no charge. Clearly, the nucleus of an atom bears a positive charge. An electron is a negatively charged particle having negative charge equal to the positive charge on a proton. Under normal conditions, the number of electrons is equal to the number of protons in an atom. Therefore, an atom is neutral as whole, the negative charge on electrons cancelling the positive charge on protons.

The above discussion shows that matter is electrical in nature i.e. it contains particles of electricity viz protons and electrons. Wheter a given body exhibits electricity (i.e. chare) or nto depends upon the relative number of these particles of electricity.

- i. If the number of protons is equal to the number of electrons in a body, the resultant charge is zero and the body will be electrically neutral. Thus the paper of this book is electrically neutral (i.e. paper exhibits no charge) because it has the same number of protons and electrons.

- ii. If from a neutral body, some electrons are removed, there occurs a deficit of electrons in the body. Consequently, the body attains a positive charge. Hence a positively charged body has deficit of electrons from the normal due share.

- iii. If a neutral body is supplied with electrons, there occurs an excess of electrons. Consequently, the body attains a negative charge. Hence a negatively charged body has an excess of electrons from the normal due share.

#### **Unit of Charge**

The charge on an electron is so small that it is not convenient to select it as the unit of charge. In practice, coulomb is used as the unit of charge. One coulomb of charge is equal to the charge on  $625 \times 10^{16}$  electrons i.e.

1 Coulomb = Charge on 625 x 10<sup>16</sup> electrons

Thus when we say that a body has a positive charge of 1 coulomb (1 C), it mans that it has a deficit of  $625 \times 10^{16}$  electrons from the normal due share.

#### **Free Electrons**

We know electrons move round the nucleus of an atom in different orbits. The electrons in the last orbit are called valence electrons. In certain substances, especially metals (e.g. copper, aluminium etc), the valence electrons are so weakly attached to their nuclei that they can be easily removed or detached. Such electrons are called free electrons. It may be noted here that all valence electrons in a metal are not free electrons. It has been found that one atom of metal can provide at the msot one of free electrons in metals. For example,  $1 \text{ cm}^3$  of copper has about  $8.5 \times 10^{22}$  free electrons at room temperature.

#### **ELECTRIC CURRENT**

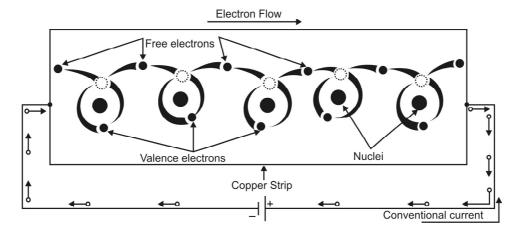

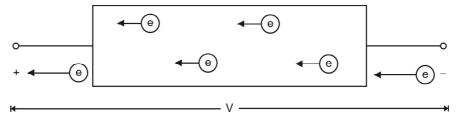

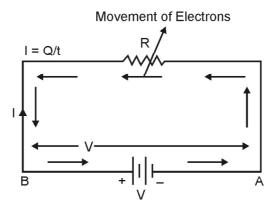

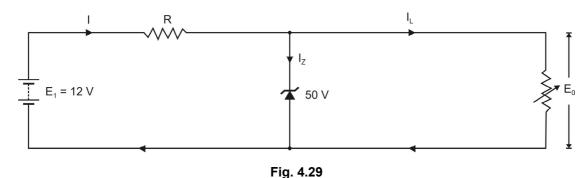

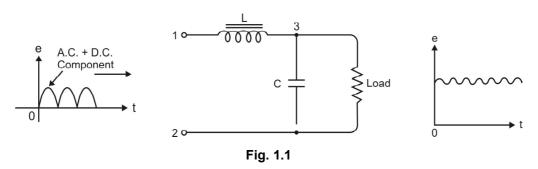

The flow of free electrons (or charge) in a definite directions is called electric current. The flow of electric current is shown in Fig. 1.1. The copper strip has a large number of free electrons. For simplicity, only the valence orbits are shown because only the valence electrons can take apart in the flow of current. When electric pressure or voltage is applied, the free electrons being negatively charged start moving towards the positive terminal round the circuit as shown in Fig. 1.1. This directed flow of electrons is called electric current.

Conventionally, the direction of electric current is taken along the direction of motion of positive charges. When current is caused by electrons (e.g. in metals), the direction of current is opposite to the direction of electron flow.

Fig. 1.1

**Note:** It is important to note that none of the practical consequences nor any of the results of computations performed in the study of electricity and electronics are in any way affected by the direction of current flow that one assumes. In this book, the direction of conventional current will be assumed.

#### **Measurement of Current**

The flow of charge in a definite direction is called electric current. It is measured by the time rate of flow of charge through the conductor. If q is the charge flowing through any cross-section of the conductor in time t, then,

Electric current,

$$I = \frac{1}{2}$$

If the rate of flow of charge varies with time, then current at any time (instantaneous current) is given by;

$$i = \frac{dq}{dt}$$

where dq is the small charge passing through any cross-section of the conductor in small time dt. The SI unit of electric current is ampere. If q = 1 C and t = 1s, then l = 1/1 = 1 ampere.

**One Ampere** of current is said to flow through a wire if at any section one coulomb of charge flows in one second.

If n electrons are passing through any cross-section of the wire in time t, then,

$$I = \frac{q}{t} = \frac{ne}{t}$$

where  $e = 1.6 \times 10^{-19} \text{C}$

#### **Electric Potential**

Just as a body raised above the ground has gravitational potential energy, similarly, a charged body has electric potential energy. When a body is charged, work is done in charging the body. This work done is stored in the body in the form of electric potential energy. The charged body has the capacity to do work by moving other charges either by attraction or repulsion. Quantitatively, electric potential is defined as under:

The electric potential at a point is the electric potential energy per unit charge.

Electric potential,

$$V = \frac{\text{Electric potential energy}}{\text{Charge}} = \frac{W}{Q}$$

The SI unit of energy or work is 1 J and that of charge is 1 C so that SI unit of electric potential is 1 J/C which is also called 1 volt.

Thus when we say that electric potential at a point is 10V, it means that if we place a charge of 1C at that point, the charge will have electric potential energy of 10J. Similarly, if we place a charge of 2C at that point, the charge will have electric potential energy of 20J. Note that potential energy per unit charge (i.e. electric potential) is 10V.

#### **Potential Difference**

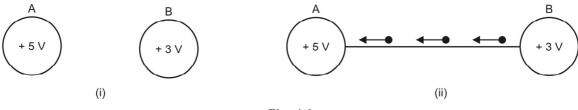

The difference in the potentials of two charged bodies is called potential difference (p.d.). Consider two bodies A and B having potentials of +5V and +3V respectively as shown in Fig. 1.3 (i). Each coulomb of charge on body A has an energy of 5 Joules while each coulomb of charge on body B has an energy of 3 Joules. Clearly, the body A is at higher potential than body B.

Fig. 1.3

If the two bodies are joined through a conductor [See Fig. 1.3 (ii)], then electrons will flow from body B to body A. When the two bodies attain the same potential, the flow of current stops. Therefore, we arrive at a very important conclusion that current will flow in a circuit if potential difference exists. No potential difference, no current flow. It may be noted that potential difference is sometime called voltage.

#### EMF. Voltage. Potential Difference

Absolute potential of a point is the work done in moving a unit positive test charge from infinity to that point. The potential difference between two points is the work done in moving a unit positive test charge from one point to the other. If we have two points A and B and it requires work to move a unti positive charge from B to A than A is said to be at higher potential with respect to B or the potential difference between points A and B is positive. When we move from point B to point A, we experience a rise in potential. Conversely, from point A to B there is a fall or potential.

The SI unit of potential difference is volt (symbol V). It is defined as the potential difference across a resistance of 1 ohm when a current of 1A is flowign in the resistance.

Since the potential difference between two points A and B may be positive or negative, it is more appropriate to write is as, say  $V_{AB}$  which means potential of point A with respect to that of point B. If A is at higher potential than B,  $V_{AB}$  is positive. Then  $V_{BA}$  (i.e. potential of point B with respect to that of A) is negative. Thus  $V_{BA} = -V_{AB}$ . The terms potential difference and voltage are synonymous.

The term emf (electromotive force) is also used instead of voltage. Strictly speaking emf is the total voltage of a source (e.g. a battery or a generarator). There would always be some voltage drop in the source itself and the voltage at the terminals of the source would be a bit less than the source emf. The voltage at the terminals is known as output voltage or terminal voltage.

#### **Electric Potential or Voltage**

A continuous path is needed before a continuous flow of electrons will occur. There is a need for some means to push these electrons around the circuit. With electrons, the force for movement is produced by an imbalance of electric charge. In order to move electrons along a conductor, some amount of work is required.

When electrons are present in the static condition, the energy stored is called "potential energy". This potential energy, stored in the form of an electric charge is imbalanced and capable of providing electrons to flow through a conductor, is expressed as "Voltage", which is a measure of potential energy per unit charge on electron. Voltage is the measure of work required to move a unit charge from one location to another, against the force which tries to keep electric charge balanced.

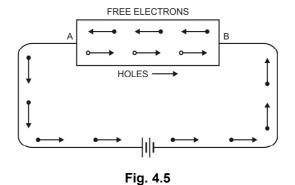

#### Why Current Flows in the Circuit

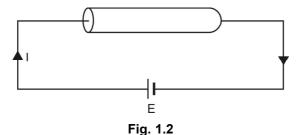

Let potential difference exists between two terminals of the resistance.

Fig. 1.4. Resistance and Potential

Due to this potential difference, one terminal is positive and other terminal is negative. Now due to positive and negative charges threre is the production of free electrons. Due to poitive and negative charges, electrons start to flow from negative side to positive side because the charge on electron is negative and negative charges repels and negative-positive charges attract each other.

Fig. 1.5. Flow of electrons on application of voltage

As the electric current is due to the flow of electrons, the current to flow in the circuits as shown in Fig. 1.5. The direction of current is opposite to flow of electrons i.e. from positive side to negative side.

In other words, if the conductor is connected across positive and negative terminals, due to the potential difference between the terminals, the current starts to flow in conductor and direction of current is from positive terminal to negative terminal.

#### **ELECTROMAGNETIC FORCE**

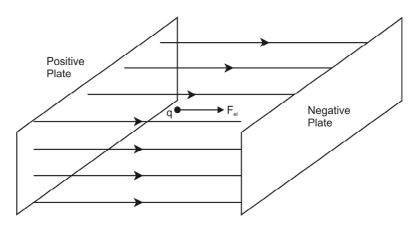

The force exerted by one particle on another by virtue of electric charge on the particle is known as electromagnetic force. An electromagnetic force is a physics concept that refers to a particular force or influence, that effect charged particles. These particles may be positively or negatively charged. The electromagnetic force of interaction that exists between certain elementary particles is regarded as a force between electric charges. Electromagnetic force acts between two electrically charged particles e.g. a negatively charged electron and a positively charged proroton attracts each other with a force which is poroportional to electric charge and inversely proportional to the square of distance between them. The presence of charged particle produces an electric field and when moving it produces a magnetic field. This field manifests itself in a force between chared particles. The difference between these forces is that for a magnetic force to act the charge must be moving, but the electric force is independent of the motion.

Fig. 1.7 shows a charged particle in an electric field. If the charged q is at point 'a' where the electric field is E, the electric force  $F_{e_1}$  on the charge 1 is

$$F_{e1} = q.E$$

The direction of the electrid field is parallel to the electric field if charge q is positive and antiparallel if it is negative.

Fig. 1.7. Electric force F<sub>e1</sub> on charge q in electric field

The magnetic force  $F_{\text{mag}}$  on charge q moving with speed v due to magnetic field B is

$$F_{mag} = qv x B$$

The total electromagnetic force on charge 1, arising from the combined electric and magnetic force is:

$$F = F_{e1} + F_{mag} = q (E + v \times B)$$

#### **ELECTRIC POWER**

The power of an electric applicance is the rate at which electrical energy is converted into other forms of energy (e.g. heat, etc.). For example, a 60 W bulb converts 60J of electrical energy into heat light each second.

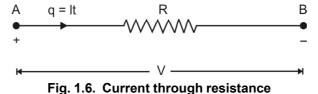

Thus referring to Fig. 1.8, as the charge q (= I t) moves from point A to B, it loses electric potential energy = qV. In other words, qV joules of electrical energy is converted into heat in t seconds.

Fig. 1.8

Any one of the three formulas can be used to calculate electric power, depending upon the problem in hand.

#### **Unit of Electric Power**

$$P = VI$$

The SI unit of p.d. is 1 V and that of current is 1 A so that SI unit of power = 1 V x 1 A = 1 V A or 1 watt (1W). Hence electric power of a circuit or device is one watt if a current of 1A flows through it when a p.d. of 1V is maintained across it.

The bigger units of electric power are kilowatt (kW) and megawatt (MW).

$$1 \text{ kW} = 1000 \text{ W}$$

;  $1 \text{ MW} = 10^3 \text{ kW} = 10^6 \text{ W}$ .

**Note.** Electric appliances are rated in terms of electric power. The faster the appliances converts electrical energy into some other from of energy, the greater the electric` power it has. Thus, in 1 second, a 100 W bulb coverts more electrical energy into heat and light than a 60 W bulb.

#### **ELECTRICAL ENERGY**

The loss of electrical potential energy in maintaining current in a circuit is called electrical energy consumed in the circuit.

Thus in Fig. 1.8 above, as the charge q (= I t) moves from point A to B, it loses electric potential energy = q V = V I t joules. This loss of electric potential is converted into heat.

We say that electrical energy consumed in t second is VIt joules.

∴ Electrical energy consumed,

$$W = VIt = I^2Rt = \frac{V^2}{R}t$$

joules

#### **Unit of Electrical Energy**

$$W = V I t = power x time$$

The SI unit of power is 1W and that of time is 1s so that SI unit of electrical energy =  $1W \times 1s = 1Ws$  or 1J.

I J (or 1Ws) energy is consumed when a device (e.g., bulb, heater, etc.) converts electrical energy to other forms at a rate of 1W for a time of 1 second.

Commercial Unit. In practice, electrical energy is measured in kilowatt-hour (kWh).

**1 kWh** energy is consumed when a device converts electrical energy to other forms at a rate of 1 kW for a time of 1 hour.

Electrical energy in kWh = Power in kW x Time in hours.

The electricity bills are made on the basis of total electrical energy consumed by the consumer. The unit for billing of electrical energy is 1k Wh. Thus when we say that a consumer has consumed 100 units, it means that electrical energy consumption is 100 kWh.

#### **Use of Power and Energy Formulas**

It has already been discussed that electric power as well as electrical energy consumed can be expressed by three formulas. While using these formulas, the following points may be kept in mind:

i. Electric Power,

$$P = I^2 R = \frac{V^2}{R}$$

watts

Electrical energy consumed,

$$W = I^2 R t = \frac{V^2}{R} t$$

joules

The above formulas apply only to resistors and to devices (e.g.,. electric bulb, heater, electric kettle etc.) where all electrical energy, consumed is converted into heat.

ii. Electric power, P = V I watts

Electrical energy consumed, W = V I t joules

#### **Electrical Materials**

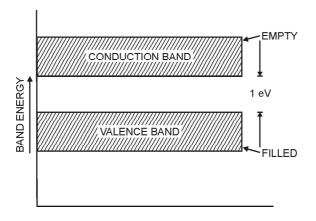

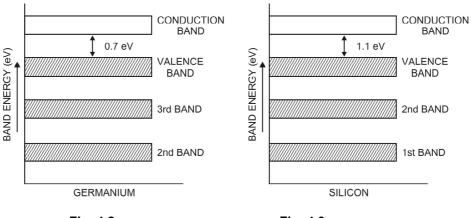

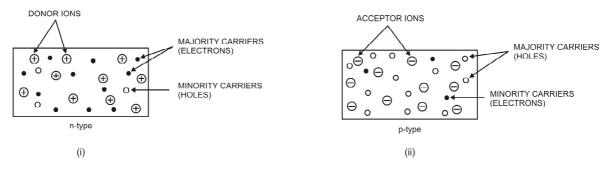

The materials used in electricity and electronics can be broadly divided into three major types viz

1. Conductors

2. Semiconductors

3. Insulators

Conductors (e.g. copper, aluminium etc.) conduct current very easily while insulators (e.g. glass, mica, paper) practically conduct no current. In other words, conductors have small resistivity and insulators have high value of resistivity. The resistivity of semiconductors (e.g. germanium, silicon etc.) lies between conductors and insulators.

#### **Conductors**

- i. Conductors are formed by metallic bonds. These bonds are based on a structure of positive metal ions surrounded by a cloud of electrons.

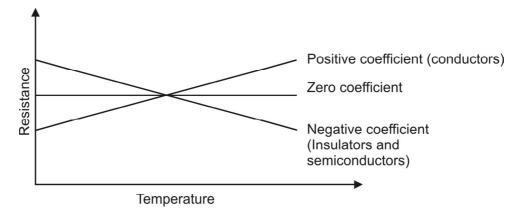

- ii. Conductors have positive termperature coefficient of resistance i.e. their resistance increases with the rise in temperature and vice-versa [see Fig. 1.9].

Fig. 1.9

iii. Conductors are used to carry current in electric circuits.

#### **Power and Energy in Resistance**

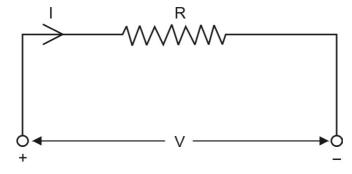

The resistor is an element, which dissipate the energy in the form of heat.

Fig. 1.10. Resistive circuit

By Ohm's law V = IR

Power at any instant  $p = VI = I^2 R$  watt

Energy at any instane  $e = \int p dt = I^2Rt$  joules

At steady state  $p = VI = I^2 Rt$  joules

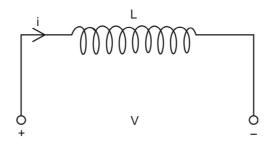

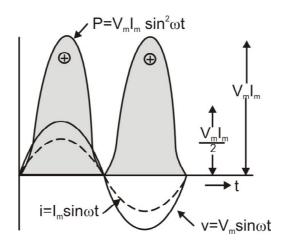

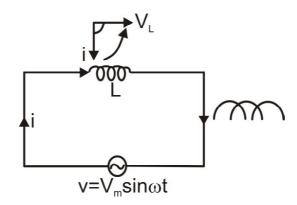

#### Power and Energy in Inductor

The indicator is an element, which stores the energy by virtue of current flowing through it.

Fig. 1.11. Inductive circuit

The voltage across the capacitor is  $V = \frac{1}{C}q$

The current through the capacitor is  $i = C \frac{dV}{dt}$

Power in capacitor

$$p = V.i = V.C \frac{dV}{dt}$$

$$p = CV = \frac{dV}{dt}$$

Energy in capacitance

$$E = C \int V \frac{dV}{dt}.dt = C \int V dc$$

$$E = \frac{1}{2}CV^2$$

joules

The energy is stored in the form of electrostatic field of capacitor and capacitor also does not dissipate any power.

| Element | Voltage    | Current                      | Power                    | Energy            |

|---------|------------|------------------------------|--------------------------|-------------------|

| R       | I.R.       | <u>V</u> R                   | I <sup>2</sup> R         | I <sup>2</sup> Rt |

| L       | L di<br>dt | $\frac{1}{L}\int V \cdot dt$ | Li <mark>di</mark><br>dt | $\frac{1}{2}Li^2$ |

| С       | 1/C∫i·dt   | C dV dt                      | CV dV/dt                 | $\frac{1}{2}CV^2$ |

Table 1.1: Properties of Circuit Elements

#### **OHM'S LAW**

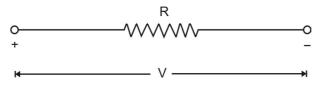

This law applies to electric to electric conduction through good conductros and may be state as follows:

The ratio of potential difference (V) between any two points on a conductor to the current (I) flowing between them, is constant, provided the temperature of the conductors does not change.

In other words,

$$\frac{V}{I} = constant$$

or  $\frac{V}{I} = R$

where R is the resistance of the ocnductor between the two points considered.

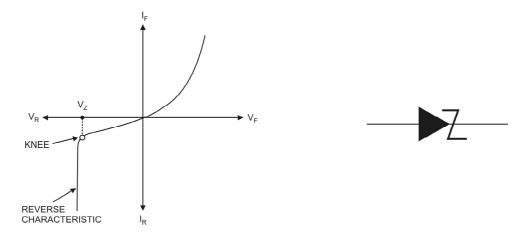

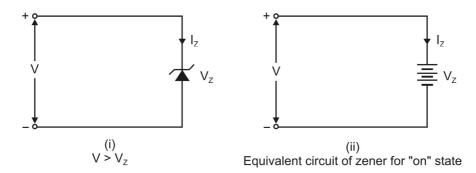

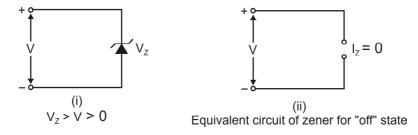

Put in another way, it simply means that provided R is kept constant, current is directly proportional to the potential difference across the ends of the conductor. However, this linear relationship between V and I does not apply to all non-metallic conductors. for example, for silicon carbide, the relationship is given by  $V = KI^m$  where K and m are constants and m is less than unity. It also does not apply to non-linear devices such as Zener diodes and voltage-regulator (VR) tubes.

#### Resistance

It may be defined as the property of a substance due to which it opposes (or restricts) the flow of electricity (i.e., electrons) through it.

Metals (as a class), acids and salts solutins are good conductors of electricity. Amongst pure metals, silver, copper and aluminium are very good conductors in the given order. This, as discussed earliear, is due to the presence of a large number of free or loosely-attached electrons in their atoms. These vagrant electrons assume a directed motion on the application of an electric potential difference. These electrons while flowing pass through the molecules or the atoms of the conductor, collide and other atoms and electrons, thereby producing heat.

Those substances which offer relatively greater difficulty or hindrance to the passage of these electrons are said to be relatively poor conductors of electricity like bakelite, mica, glass, rubber, p.v.c. (polyvinyle chloride) and dry wood etc. Amongst good insulators can be included fibrous sunstances such as paper and cotton when dry, mineral oils free from acids and water, ceramics like hard porcelain and asbestos and many other plastics besides p.v.c. It is helpful to remember that electric friction is similar to friction in Mechanics.

#### The Units of Resistance

The practical unit of resitance is ohm. A conductor is said to have a resistance of one ohm if it permits one ampere current to flow through it when one volt is impressed across its terminals.

For insulators whose resistances are very high, a much bigger unit is used i.e., mega-ohm =  $10^6$  ohm (the prefix 'mega' or mego meaning a million) or kilo-ohm =  $10^3$  ohm (kilo means thousand). In the case of very small resistances, smaller units like milli-ohm =  $10^{-3}$  ohm or micro-ohm =  $10^{-6}$  ohm are used. The symbol for ohm is  $\Omega$ .

| Prefix | Its meaning    | Abbreviation | Equal to         |

|--------|----------------|--------------|------------------|

| Mega-  | One million    | M Ω          | 10 <sup>6</sup>  |

| Koli-  | One thousand   | kΩ           | 10 <sup>3</sup>  |

| Centi- | One hundredth  | -            | -                |

| Milli- | One thousandth | m $\Omega$   | 10 <sup>-3</sup> |

| Micro- | One millionth  | $\mu\Omega$  | 10-6             |

Table 1.2. Multiples and Sub-multiples of Ohm

#### Laws of Resistance

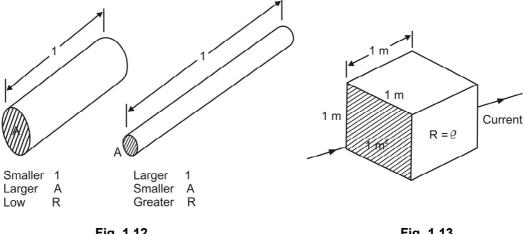

The resistance R offered by a conductor depends on the following factors:

- i. It varies directly as its length, I

- ii. It varies inversely as the cross-section A of the conductor.

- iii. It depends on the nature of the material.

- iv. It also depends on the temperature of the conductor.

Fig. 1.12 Fig. 1.13

Neglecting the last factor for the time being, we an say that

$$R \propto \frac{I}{A} \text{ or } R = \rho \frac{I}{A}$$

wehre  $\rho$  is a constant depending on the nature of the material of the conductor and is known as its specific resistance or resistivity.

I = 1 metre and A = 1 metre<sup>2</sup>, then R =

$$\rho$$

(Fig. 1.13)

Hence, specific resistance of a material may be defined as the resistance between the opposite faces of a metre cube of that material.

#### **Units of Resistivity**

From Eq. (i), we have

$$\rho = \frac{AR}{I}$$

$$\rho = \frac{A\,metre^2\,x\,R\,ohm}{I\,metre} = \frac{AR}{I}\,ohm - metre$$

Hence, the unit of resistivity is ohm-metre ( $\Omega$ -m).

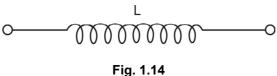

#### Inductance

The inductance is the property of a circuit element by virtue of which it opposes the change of current through it and is capable to store electric energy in the form of magentic field. Inductance has no meaning unless the current through it changes with respect to time.

Inductors react against change in current by dropping voltage in the polarity necessary to oppose the change. When an inductor is faced with an increasing current, it have drop in voltage (load) as it absorbs energy. When an inductor is faced with a decreasing current, it acts as a source, which creates voltage as it release stored energy.

The inductance parameter depends upon the geometry, physical dimension and property of magnetic medium. The unit of inductance is Henry (H). The ability of an inductor is to store energy in the form of magnetic field, is called inductance.

$$L = \frac{N^2 \mu A}{I}$$

When N is number of turns, I is mean length of the core, A is cross-sectional area of the acore and  $\mu$  is permeability of the material of core. The inductor has no resistance. The energy is stored by the inductor in its magenetic field. Resistance parameter dissipate electrical energy but the inductance parameter does not dissipate energy but it stores the same.

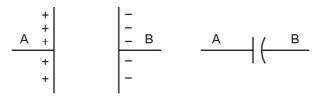

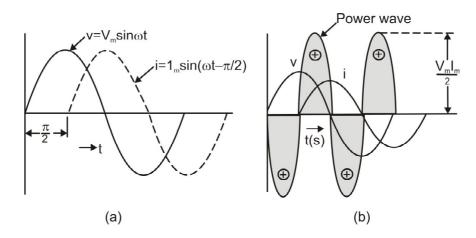

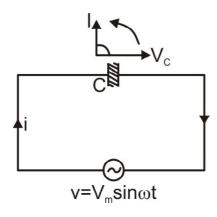

#### Capacitance

The capacitance is the propterty of circuit element which appears only when time varying potential is applied across its terminals. A capacitor consists of two conducting surfaces separated by a layer of an insulating medium called dielectric. The use of capacitor is to store electric energy by means of electrostatic stress in dielectric.

Capacitors react against changes in voltage by supplying current in the direction necessary to oppose the change. When capacitor is faced with an increasing voltage, it acts as a load and draw current as it absorbs energy. When capacitor is faced with decreasing voltage, it acts as a source and supply current as it releases stored energy.

The capacitance is the amount of charge required to create a unit potential difference between its plates.

Fig. 1.15. Capacitor and its symbol

Let Q coulomb is the charge on one of two plates of capacitor and if potential difference of V volt's between the plates, then capacitance is given as

$$C = \frac{Q}{V} = \frac{Charge \, on \, one \, plate}{Potential \, difference \, between \, two \, plates}$$

The ability of a capacitor is to store energy in the form of an electric field, is called capacitance. The unit of capacitance is Farad (F). One Farad is defined as the capacitance which requires a charge of one coulomb to establish a potential difference of one volt between its plates.

The capacitane depends on the area, distance between the two plates and permitivity of the medium between the plates.

$$C = \frac{\in A}{d} = Farad$$

Where  $\in$  is permittivity of the medium between the plates, A is area of plates and d is the distance between two plates. The capacitance is the property which delay any change of voltage across it i.e. oppose the change of voltage.

#### **Classification of Circuit Elements**

The resistor, inductor, capacitor, etc. are called circuit elements. The circuit elements are classified as follows:

#### **Active Elements**

The elements which are source of energy and always supply energy to the network are called active elements. The energy source can be supplying voltage or current. An element which can increase the power level of the circuit, is known as active element. A transistor is an active element as it can amplify the power level in the circuit. Transformer is not an active element as it can not modify the power level.

**Examples:** Batteries, cell, alternators, etc.

#### **Passive Elements**

The elements which either dissipate or store the energy are called passive elements. These elements have the property of absorbing/dissipating or storing energy. These are able to return the energy previously stored in them. These elements are not able to return energy more than that stored in them.

**Examples:** Resistance, inductance, capacitance, etc.

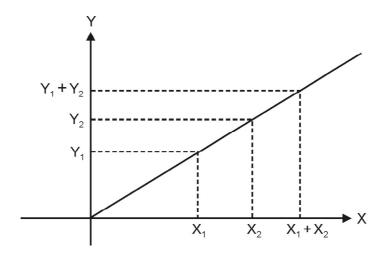

#### **Linear Elements**

Linear elements are elements, whose output is directly proportional to the input. Consider an element A. Let for  $X_1$  input, output is  $Y_1$ , for  $X_2$  input, output is  $Y_2$ . Then if the element is linear and  $X_1 + X_2$  is input, then output must be  $Y_1 + Y_2$ . This is known as the superposition principle and the elements which follow superposition principle are called linear elements. In electrical term, the elements whose value do not change with the change in current or voltage are called linear elements.

Fig. 1.16. Characteristics of Linear Parameter

Examples: Pure R, L, C, etc.

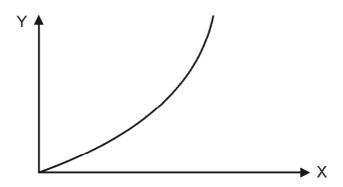

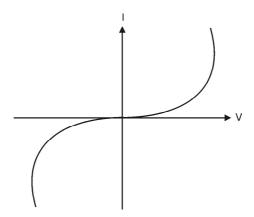

#### **Non-linear Elements**

The elements which do not follow superposition principle are non-linear elements. In the non-linear elements the output is not directly proportional to the input.

Examples: Diodes, choke, etc.

Fig. 1.17. Characteristics of Non-Linear System

#### **Lumped Parameters**

If any parameter can be concentrated (lumped) at one point irrespective of their physical size and properties, without affecting the electrical properties of the parameter, then it is called as lumped parameter.

**Examples:** Resistance, inductance, capacitance, etc.

#### **Distributed Parameter**

If the parameter cannot be assumed to be lumped at one point and it is distributed all over the circuit, is called 'Distributed Parameter'. Sometimes when we are interested in the intermediate values or point to point values of the electrical signal, then the element is said to be distributed.

**Examples:** Transmission line, etc.

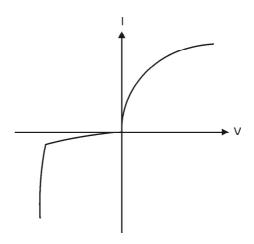

#### **Bilateral Elements**

The elements are assumed to be bilateral, in which voltage and current relationship are same irrespective of the direction of flow of current i.e. properties of elements does not depend on direction of flow of current. The behaviour of the element is equal in either direction. The V-I curve will be same in both the direction for bilateral element.

Fig. 1.18. V-I Characteristic of Bilateral Elements

**Examples:** Resistance (because the V/I ratio is alway R irrespective of direction of flow of current), etc.

#### **Unilateral Elements**

The elements are assumed to be unilateral, in which voltage and current relationship are not same if the direction of current is changed i.e. the voltage and current are different for two possible directions of flow of current. The behaviour of the element is unequal in either directions. The V-I curve will be different in both directions for unilateral elements (I and III quadrant).

Fig. 1.19. V-I Characteristic of Unilateral Elements

Examples: Diode, etc.

#### **Time-Invariant Elements**

The elements which do not change their values with respect to tiem are called time-invariant elements. In these elements, the response with remain same to certain input irrespective of time of application of input i.e. the value of that element is same (constant) at all time.

**Example:** Inductance, etc.

#### **Time-Varying Elements**

The elements whose value change with respect to time are called time-varying elements. In these the response to certain input depend on time of application of input. The value of the element is different at different time.

**Example:** Resistance, etc.

#### **ELECTRICAL POWER AND ENERGY**

When a potential difference (V volts) is applied across a resistance, a current (I amperes) flows through it for a particular time period (t seconds). A work is said to be done for moving electrons and this work done is called electrical energy.

The total amount of work done in an electric circuit is called electrical energy.

$$V = \frac{Workdone}{O}$$

i.e. work done or electrical energy = V.Q

as

$$I = \frac{G}{t}$$

so work done =

$$V.I.t = \frac{V^2}{R}t$$

Fig. 1.20. Electrical Energy

The basic unit of electrical energy is joule or watt-second.

electrical energy = 1 joule

The energy is said to be joule if one ampere current flows through the circuit for one second when a potential difference of 1 volt is applied across it. The other unit of electrical energy is kilowatt-hour (kW-h). 1kWh = 1000 x 60 x watt-second = 36 x 10<sup>5</sup> Watt-sec or joules.

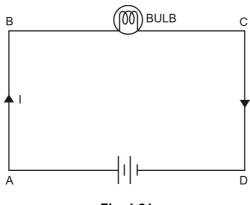

#### **DIRECT CURRENT**

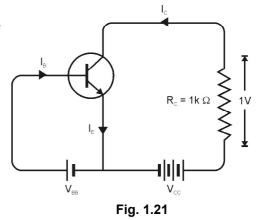

The current that always flows in one direction is called direct current (d.c.). The current supplied by a cell/ battery or d.c. generator is direct current. Thus in Fig. 1.21, the battery supplies direct current to the bulb. The direction of current is along ABCDA and always flows in this direction. Note that direct current means steady direct current unless stated otherwise.

#### D.C. Circuit

The closed path followed by direct current is called a D.C. circuit. A D.C. circuit essentially consists of a source of direct voltage (e.g. battery), the conductors used to carry current and the load. Fig. 1.21 shows a torch bulb (i.e. load) connected to a battey through conducting wires. The direct current starts from the po; sitive terminal of the battery and comes back to the starting point via the load. The direct current follows the closed path ABCDA and hence ABCDA is a D.C. circuit. The load for a D.C. circuit is usually a resistance. In a D.C. circuit, loads (i.e. resistances) may be connected in series or parallel or series-parallel.

Fig. 1.21

#### **Resistors in Series**

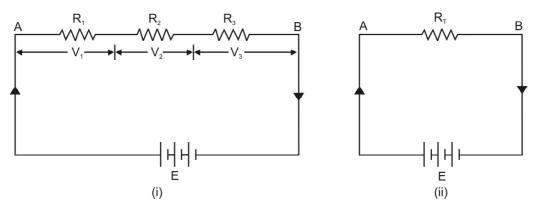

A number of resistors are said to be connected in series if the same current flows through each resistor and there is only one path for the current flow throughout. Consider three resistors of resistances  $R_1$ ,  $R_2$  and  $R_3$  connected in series across a battery of E volts as shown in Fig. 1.22 (i). Then total resistance  $R_7$  is given by,

$$R_{T} = R_{1} + R_{2} + R_{3}$$

Fig. 1.22

Hence when a number of resistances are connected in series, the total or equivalent resistance is equal to the sum of the individual resistances. Thus we can replace the series connected resistors shown in Fig. 1.22 (i) by a single resistor  $R_T$  (=  $R_1$  +  $R_2$  +  $R_3$ ) as shown in Fig. 1.22 (ii). This will enable us to calculate the circuit current easily (I =  $E/R_T$ ).

i. When resistors are connected in series, the total circuit resistance increases.

ii.

$$R_{T} = R_{1} + R_{2} + R_{3}$$

or

$$\frac{R_{T}}{V^{2}} = \frac{R_{1}}{V^{2}} + \frac{R_{2}}{V^{2}} + \frac{R_{3}}{V^{2}}$$

or

$$\frac{1}{P_{T}} = \frac{1}{P_{1}} + \frac{1}{P_{2}} + \frac{1}{P_{3}}$$

where  $P_T$  is the total power dissipated by the series circuit and  $P_1$ ,  $P_2$  and  $P_3$  are the powers dissipated by individual resistors.

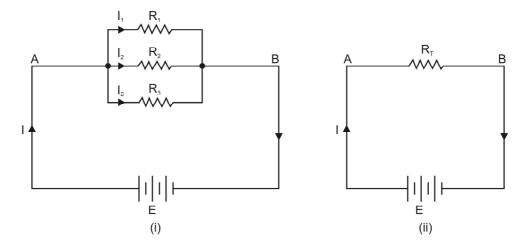

#### **Resistors in Parallel**

A number of resistors are said to be connected in parallel if voltage across each resistor is the same and there are as many paths for current as the number of resistors. Consider three resistors of resistances  $R_1$ ,  $R_2$  and  $R_3$  connected in parallel across a battery of E volts as shown in Fig. 1.23 (i). Then total resistance  $R_{T}$  is given by;

$$\frac{1}{R_T} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}$$

Fig. 1.23

Hence when a number of resistnaces are connected in parallel, the reciporocal of the total resistance is equal to the sum of reciprocals of individual resistances. Again, we can replace the parallel connected resistors shown in Fig. 1.23 (i) by a single resistor  $R_{\tau}$  shown in Fig. 1.23 (ii).

- i. When resistors are connected in parallel, the total circuit resistance decreases.

- ii. The total resistance of a parallel circuit is always less than the smallest of the resistances. For example, if three resistors of  $1\Omega$ ,  $3\Omega$  and  $4\Omega$  are connected in parallel, the total resistance will be less than  $1\Omega$ .

- iii. If n resistors, each or resistance R, are connected in parallel, then total resistance  $R_{\tau} = R/n$ .

iv.

$$\frac{1}{R_T} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}$$

or

$$\frac{V^2}{R_T} = \frac{V^2}{R_1} + \frac{V^2}{R_2} + \frac{V^2}{R_3}$$

or

$$R_T = R_1 + R_2 + R_3$$

where  $P_T$  is the total power dissipated by the parallel circuit and  $P_1$ ,  $P_2$  and  $P_3$  are the powers dissipated by individual resistors.

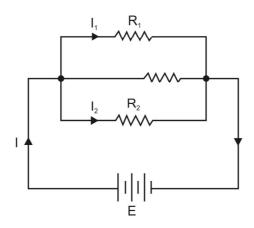

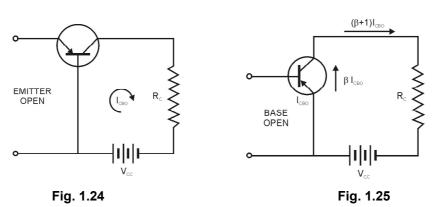

#### Two Resistors in Parallel

A frequent special case of parallel resistors is a circuit that contains two resistors in parallel as shown in Fig. 1.24. The total circuit current I divides into two parts; I, flowing through R, and I, flowing through R,

Fig. 1.24

i. **Total Resistance:**

$$\frac{1}{R_{T}} = \frac{1}{R_{1}} + \frac{1}{R_{2}} = \frac{R_{2} + R_{1}}{R_{1}R_{2}}$$

or

$$R_{T} = \frac{R_{1}R_{2}}{R_{1} + R_{2}} \text{ i.e., } \frac{Product}{Sum}$$

Thus, if two resistances of  $3\Omega$  and  $6\Omega$  are connected in parallel, then their total or equivalent resistance R is

$$R = \frac{3x6}{3+6} = \frac{18}{9} = 2\Omega$$

$$\begin{aligned} \text{ii.} \quad & \textbf{Branch Currents}: \qquad & E = IR_T = I\frac{R_1R_2}{R_1 + R_2} \\ & \textbf{Now} \qquad & I_1 = \frac{E}{R_1} = \left(I\frac{R_1R_2}{R_1 + R_2}\right)\frac{1}{R_1} = I\frac{R_2}{R_1 + R_2} \\ & \therefore \qquad & I_1 = Ix\frac{R_2}{R_1 + R_2} \\ & \text{Similarly,} \qquad & I_2 = Ix\frac{R_1}{R_1 + R_2} \end{aligned}$$

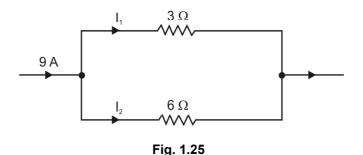

Thus referring to Fig. 1.25, the currents in the two branches are:

$$I_1 = 9 \times \frac{6}{3+6} = 6 \text{ A}$$

$$I_2 = 9 \times \frac{3}{3+6} = 3 A$$

#### **Advantages of Parallel Circuits**

The most useful property of a parallel circuit is the fact that potential differences has the same value between the terminals of each branch of parallel circuit. This feature of the parallel circuit offers the following advantages:

- i. The appliances rated for the same voltage but different powers can be connected in parallel without disturbing each other's performance. Thus a 230V, 230W TV receiver can be operated independently in parallel with a 230V, 40W lamp.

- ii. If a break occurs in any one of the branch circuits, it will have no effect on other branch circuits.

Due to above advantages, electrical appliances in homes are connected in parallel. We can switch on or off any light or appliances without affecting other lights or appliances.

#### Maxwell,,s Loop Current Method

This method which is particularly well-suited to coupled circuit solutions employs a system of loop or mesh currents instead of branch currents (as in Kirchhoff's laws). Here, the currents in different meshes are assigned continuous paths so that they do not split at a junction into branch currents. This method eliminates a great deal of tedious work involved in the branch-current method and is best suited when energy sources are voltage sources rather than current sources. Basically, this method consists of writing loop voltage eqautions by Kirchhoff's voltage law in terms of unknown loop currents. As will be seen later, the number of independent equations to be solved reduces from b by Kirchhoff's laws to b-(j-1) for the loop current method where b is the number of branches and j is the number of junctions in a given network.

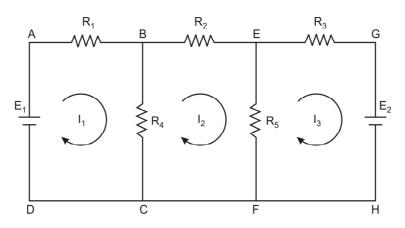

Fig. 1.26

Fig. 1.26 shows two batteries  $E_1$  and  $E_2$  connected in a network consisting of five resistors. Let the loop currents for the three meshes be  $I_1$ ,  $I_2$  and  $I_3$ . It is obvious that current through  $R_4$  (when considered as a part of

the first loop) is  $(I_1 - I_2)$  and that through  $R_s$  is  $(I_2 - I_3)$ . However, when  $R_4$  is considered part of the second loop, current through it is  $(I_2 - I_3)$ . Similarly, when  $R_5$  is considered part of the third loop, current through it is  $(I_3 - I_2)$ . Applying Kirchhoff's voltage law to the three loops, we get,

$$\begin{split} E_1 - I_1 R_1 - R_4 & (I_1 - I_2) = 0 \quad \text{or} \quad I_1 & (R_1 + R_4) - I_2 R_2 - E_1 = 0 \\ \text{Similarly,} \quad - I_2 R_2 - R_5 & (I_2 - I_3) - I_2 - I_1) = 0 \\ \text{or} \qquad \qquad I_2 R_4 - I_2 & (R_2 + R_4 + R_5) + I_3 R_5 = 0 \\ \text{Also} \qquad - I_3 R_3 - E_2 - R_5 & (I_3 - I_2) = 0 \quad \text{or} \quad I_2 R_5 - I_3 & (R_3 + R_5) - E_2 = 0 \\ & \dots \log 3 \end{split}$$

The above three equations can be solved not only to find loop currents but branch currents as well.

#### **Mesh Analysis Using Matrix Form**

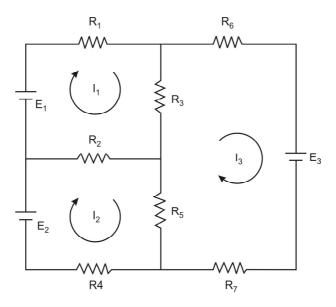

Consider the network of Fig. 1.27, which contains resistances and independent voltage sources and has three meshes. Let the three mesh currents be designated as  $I_1$ ,  $I_2$  and  $I_3$  and all the three may be assumed to flow in the clockwise direction for obtaining symmetry in mesh equations.

Fig. 1.27

Applying KVL to mesh (i), we have

$$E_1 - I_1 R_1 - R_3 (I_1 - R_2 I_2 - R_3 I_3 = E_1$$

or

$$(R_1 + R_2 + R_3) I_1 - R_2 I_2 - R_3 I_3 = E_1$$

Similarly, from mesh (ii) we have

$$E_2 - R_2 (I_2 + I_1) - R_5 (I_2 - I_3) - I_2 R_4 = 0$$

or

$$R_2I_1 + (R_2 + R_4 + R_5)I_2 - R_5I_3 = E_2$$

Applying KVL to mesh (iii), we have

$$E_3 - I_3 R_7 - R_5 (I_3 - I_2) - R_3 (I_3 - I_1) - I_3 R_6 = 0$$

or

$$R_3I_1 - R_5I_2 + (R_3 + R_5 + R_6 + R_7)I_3 = E_3$$

It should be noted that signs of different items in the above three equations have been so changed as to make the items containing self resistances positive (please see further).

The matrix equivalent of the above three equations is

$$\begin{bmatrix} +\left(R_{1}\!+\!R_{2}\!+\!R_{3}\right) & -R_{2} & -R_{3} \\ -R_{2} & +\left(R_{2}\!+\!R_{4}\!+\!R_{5}\right) & -R_{5} \\ -R_{3} & R_{5} & +\left(R_{3}\!+\!R_{5}\!+\!R_{6}\!+\!R_{7}\right) \end{bmatrix} \begin{bmatrix} I_{1} \\ I_{2} \\ I_{3} \end{bmatrix} = \begin{bmatrix} E_{1} \\ E_{2} \\ E_{3} \end{bmatrix}$$

It would be seen that the first item is the firs row i.e.  $(R_1 + R_2 + R_3)$  represents the self resistance of mesh (i) which equals the sum of all resistance in mesh (i). Similarly, the second item in the first row represents the

mutual resistance between meshes (i) and (ii) i.e. the sum of the resistance common to mesh (i) and (ii). Similarly, the third item in the first row represents the mutual-resistance of the mesh (i) and mesh (ii).

The item  $E_1$ , in general, represents the algebraic sum of the voltage of all the above sources acting around mesh (i). Similar is the case with  $E_2$  and  $E_3$ . The sign of the e.m.f.'s is the same as discussed in Art. 2.3 i.e. while going along the current, if we pass from negative to the positive terminal of a battery, then its e.m.f. is taken positive. If it is the other way around, then battery e.m.f. is taken negative.

In general, let

R<sub>11</sub> = self-resistance of mesh (i)

$R_{22}$  = self-resistance of mesh (ii) i.e. sum of all resistance in mesh (ii)

R<sub>33</sub> = Self-resistance of mesh (iii) i.e. sum of all resistance in mesh (iii)

$R_{12}$  =  $R_{21}$  = - [Sum of all the resistances common to meshes (i) and (ii)]

$R_{23}$  =  $R_{32}$  = – [Sum of all the resistances common to meshes (ii) and (iii)]

$R_{31} = R_{13} = -$  [Sum of all the resistances common to meshes (i) and (iii) Using these symbols, the generalized form of the above matrix equivalent can be written as

$$\begin{bmatrix} R_{11} & R_{12} & R_{13} \\ R_{21} & R_{22} & R_{23} \\ R_{31} & R_{31} & R_{33} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \end{bmatrix} = \begin{bmatrix} E_1 \\ E_2 \\ E_3 \end{bmatrix}$$

If there are m independent meshes in any liner network, then the mesh equations can be written in the matrix form as under:

$$\begin{bmatrix} R_{11} & R_{12} & R_{13} & ... & R_{1m} \\ R_{21} & R_{22} & R_{23} & ... & R_{2m} \\ ... & ... & ... & ... & ... \\ ... & ... & ... & ... & ... \\ R_{31} & R_{31} & R_{33} & ... & R_{3m} \end{bmatrix} \begin{bmatrix} I_2 \\ I_2 \\ ... \\ I_m \end{bmatrix} = \begin{bmatrix} E_1 \\ E_2 \\ ... \\ ... \\ E_m \end{bmatrix}$$

The above equations can be written in a more compact form as  $[R_m][I_m] = [E_m]$ . It is known as Ohm's law in matrix form.

In the end, it may be pointed out that the directions of mesh currents can be selected arbitrarily. If we assume each mesh current to flow in the clockwise direction, then

i. All self-resistances will always be positive and (ii) all mutual resistance will always be negative. We will adapt this sign convention in the solved examples to follow.

The abovemain advantage of the generalized form of all mesh equations is that they can be easily remembered because of their symmetry. Moreover, for any given network, these can be written byinspection and then solved by the use of determinants. It eliminates the tedium of deriving simultaneous equations.

#### **NODAL ANALYSIS WITH SOURCES**

The node-equation method is based directly on Kirchhoff's current law unlike loop-current method which is based on Kirchhoff's voltage law. However, like loop current method, nodal method also has the advantage that a minimum number of equations need be written to determine the unknown quantities. Moreover, it is particularly suited for networks having many parallel circuits with common ground connected such as electronic circuits.

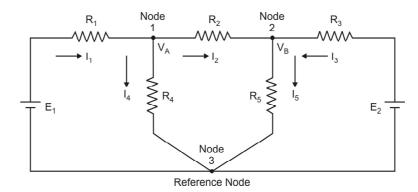

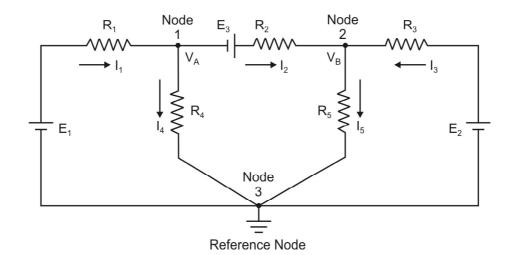

Fig. 1.28

For the application of this method, every junction in the network where three or more branches meet is regarded a node. One of these is regarded as the reference node or datum node or zero-potential node. Hence the number of simultaneous equations to be solved becomes (n - 1) where n is the number of independent nodes. These node equations often become simplified if all voltage sources are converted into current sources.

#### **First Case**

Consider the circuit of Fig. 1.28 which has three nodes. One of these i.e. node 3 has been taken in as the reference node.  $V_A$  represents the potential of node 1 with reference to the datum node 3. Similarly,  $V_B$  is the potential difference between node 2 and node 3. Let the current directions which have been chosen arbitrary be as shown.

For node 1, the following current equation can be written with the help of KCL.

$$I_{1} = I_{4} + I_{2}$$

Now

$$I_{1}R_{1} = E_{1} - V_{A} \quad \therefore \quad I_{1} = (E_{1} - V_{A})/R_{1} \qquad ...(i)$$

Obviously,

$$I_{4} = V_{A}/R_{4} \quad \text{Also, } I_{2}R_{2} = V_{A} - V_{B} \quad (V_{A} > V_{B})$$

$$I_{2} = (V_{A} - V_{B})/R_{2}$$

Substituting these values in Eq. (i) above, we get

$$\frac{E1-V_{A}}{R_{1}} = \frac{V_{A}}{R_{4}} + \frac{V_{A}-V_{B}}{R_{2}}$$

Simplifying the above, we have

$$V_A \left( \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_4} \right) - \frac{V_B}{R_2} - \frac{E_1}{R_1} = 0$$

...(ii)

The current equation for node 2 is 15 = 12 + 13

or

$$V_{B}\left(\frac{1}{R_{2}} + \frac{1}{R_{3}} + \frac{1}{R_{5}}\right) - \frac{V_{A}}{R_{2}} - \frac{E_{2}}{R_{3}} = 0 \qquad ...(iv)$$

Though the above nodal equations (ii) and (iii) seem to be complicated, they employ a very simple and systematic arrangement of terms which can be written simply by inspection. Eq. (ii) at node 1 is represented by

- 1. The product of node potential  $V_A$  and  $(1/R_1 + 1/R_4)$  i.e. the sum of the reciprocals of the branch resistance connected to this node.

- 2. Minus the ratio of adjacent potential  $V_{R}$  and the interconnecting resistance  $R_{p}$ .

- 3. Minus ratio of adjacent battery (or generator) voltage E, and interconnecting resistance R,.

- All the above set to zero.

Same is the case with Eq. (iii) which applies to node 2.

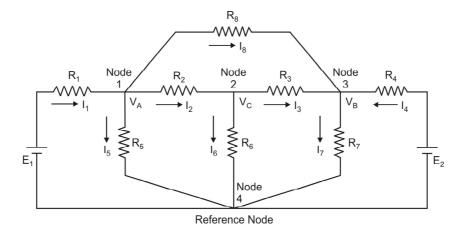

Fig. 1.29

Using conductances instead of resistances, the above two equations may be written as

$$V_A (G_1 + G_2 + G_4) - V_B G_2 - E_1 G_1 = 0$$

$V_B (G_2 + G_3 + G_5) - V_A G_2 - E_2 G_3 = 0$

To emphasize the procedure given above, consider the circuit of Fig. 1.29.

The three node equations are  $V_A \left( \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_5} + \frac{1}{R_8} \right) - \frac{V_C}{R_2} - \frac{V_B}{R_8} - \frac{E_1}{R_1} = 0$  (nodel 1)

$$V_{C}\left(\frac{1}{R_{1}} + \frac{1}{R_{3}} + \frac{1}{R_{6}}\right) - \frac{V_{A}}{R_{2}} - \frac{V_{B}}{R_{3}} = 0$$

(nodel 2)

$$V_{B}\left(\frac{1}{R_{3}} + \frac{1}{R_{4}} + \frac{1}{R_{7}} + \frac{1}{R_{8}}\right) - \frac{V_{C}}{R_{3}} - \frac{V_{A}}{R_{8}} - \frac{E_{4}}{R_{4}} = 0$$

(nodel 3)

After finding different node voltages, various currents can be calculated by using Ohm's law.

#### **Second Case**

Now, consider the case when a third battery of e.m.f.  $E_3$  is connected between nodes 1 and 2 as shown in Fig. 1.30.

Fig. 1.30

It must be noted that as we travel from node 1 to node 2, we go from the -ve terminal of  $E_3$  to its +ve terminal. Hence, according to the sign convention given in Art.2.3,  $E_3$  must be taken as positive. However, if we travel from node 2 to node 1, we go from the +ve to the -ve terminal of  $E_3$ . Hence, when viewed from node 2,  $E_3$  is taken negative.

#### For Node 1

Now,

$$I_{1} = \frac{I_{1} - I_{4} - I_{2} = 0 \text{ or } I_{1} = I_{4} + I_{1} - \text{as per KCL}}{R_{1}}; I_{2} = \frac{V_{A} + E_{3} - V_{B}}{R_{2}}; I_{4} = \frac{V_{A}}{R_{4}}$$

$$\therefore \qquad \frac{E_{1} - V_{A}}{R_{1}} = \frac{V_{A}}{R_{4}} + \frac{V_{A} + E_{3} - V_{B}}{R_{2}}$$

or

$$V_{A} \left(\frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}}\right) - \frac{E_{1}}{R_{1}} - \frac{V_{B}}{R_{2}} + \frac{E_{2}}{R_{2}} = 0$$

It is exactly the same expression as given under the First Case discussed above except for the additional term involving  $E_3$ . This additional term is taken as  $+E_3/R_2$  (and not as  $-E_3/R_2$ ) because this third battery is so connected that when viewed from mode1, it represents a rise in voltage. Had it been connected the other way around, the additional term would have been taken as  $-E_3/R_2$ .

#### For Node 2

$$I_{2} + I_{3} - I_{5} = 0 \quad \text{or} \quad I_{2} + I_{3} = I_{5} \quad -\text{ as per KCL}$$

Now, as before,

$$I_{2} = \frac{V_{A} + E_{3} - V_{B}}{R_{2}}, I_{3} = \frac{E_{2} - V_{B}}{R_{3}} = \frac{V_{B}}{R_{5}}$$

$$\therefore \qquad \frac{V_{A} + E_{3} - V_{B}}{R_{2}} + \frac{E_{2} - V_{B}}{R_{3}} = \frac{V_{B}}{R_{5}}$$

On simplifying, we get

$$V_{B} \left(\frac{1}{R_{2}} + \frac{1}{R_{3}} + \frac{1}{R_{5}}\right) - \frac{E_{2}}{R_{3}} - \frac{V_{A}}{R_{2}} + \frac{E_{3}}{R_{2}} = 0$$

As seen, the additional terms is  $-E_3/R_2$  (and not  $+E_3/R_2$ ) because as viewed from this node,  $E_3$  represents a fall in potential.

It is worth repeating that the additional term in the above Eq. (i) and (ii) can be either  $+E_3/R_2$  or  $-E_3/R_2$  depending on whether it represents a rise or fall of potential when viewed from the node under consideration.

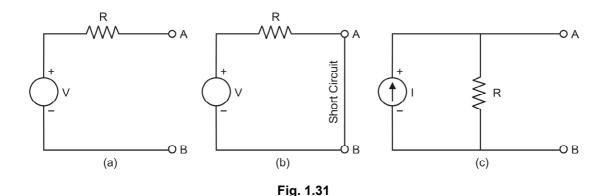

#### **SOURCE CONVERSION**

A given voltage with a series resistnace can be converted into (or replaced by) an equivalent current source with a parallel resistance. Conversely, a current source with a parallel resistance can be converted into a voltage source with a series resistance. Suppose, we want to covnert the voltage source of Fig. 1.31 (a) into an equivalent current source. First, we will find the value of current supplied by the source when a 'short' is put across in terminals A and B as shown in Fig. 1.31 (b). This current is I = V/R.

A current source supplying this current I and having the same resistance R connected in parallel with it represents the equivalent source. It is shown in Fig. 1.31 (c). Similarly, a current source of I and a parallel resistance R can be converted into a voltage source of voltage V = IR and a resistance R in series with it. It should be kept in mind that a voltage source-series resistance combination is equivalent to (or replaceable by) a current source-parallel resistance combination if, and only if their

- 1. respetive open-circuit voltages are equal, and

- 2. respective short-circuit currents are equal.

For example, in Fig. 1.31(a), voltage across terminals A and B when they are open (i.e. open-circuit voltage  $V_{\rm oc}$ ) is V itself because there is no drop across R. Short-circuit current across AB = I = V/R.

Now, take the circuit of Fig. 1.31(c). the open-circuit voltage across AB = drop across R = IR = V. If a short is placed across AB, whole of I passes through it because R is completely shorted out.

#### **Ideal Constant-Current Source**

It is that voltage whose internal resistance is infinity. In practice, it is approachaed by a source which posses very high resistance as compared to that of the external load resistance. Let the 6-V battery or voltage source have an internal resisance of  $1M\Omega$  and let the load resistance vary from 20K to 200K. The current supplied by the source varies from 6.1/1.02 = 5.7  $\mu A$  to 6/1.2 = 5  $\mu A$ . As seen, even when load resistance increases 10 times current decreases by 0.9  $\mu A$ . Hence, the source can be considered, for all practical purposes, to be a constant-current source.

#### **Superposition Theorem**

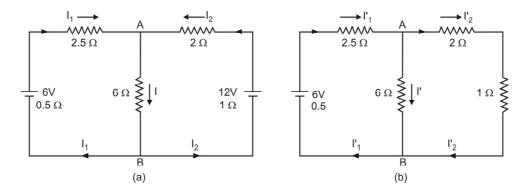

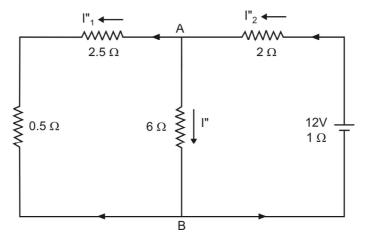

Fig. 1.32

According to this theorem if there are a number of e.m.fs. acting simultaneously in any linear bilateral network, then each e.m.f. acts independently of the others i.e. as if the other e.m.fs. did not exist. The value of current in any conductor is the algebraic sum of the currents due to each e.m.f. Similarly, voltage across any conductor is the algebraic sum of the voltages which each e.m.f. would have produce while acting singly. In other words, current in or voltage across, any conductor of the network is obtained by sumperimposing the currents and voltages due to each e.m.f. in the network. It is important to keep in mind that this theorem is applicable only to linear networks where current is linearly related to voltage as per Ohm's law.

Fig. 1.33

Hence, this theorem may be stated as follows:

In a network of linear resistances containing more than one generator (or source of e.m.f.), the current which flow at any point is the sum of all the currents which would flow at that point if each generator where considered separately and all the other generators replaced for the time being byresistances equal to their internal resistances.

#### **Explanation**

In Fig. 1.32 (a)  $I_1$ ,  $I_2$  and  $I_3$  represent the values of currents which are due to the simultaneous action of the two sources of e.m.f. in the network. In Fig. 1.32 (b) are shown the current values which would have been obtained if left-hand side battery had acted alone. Similarly, Fig. 1.33 represents conditions obtained when right-hand side battery acts alone. By combining the current values of Fig. 1.32 (b) and 1.33 the actual values of Fig. 1.32 (a) can be ontained.

Obviously,

$$I_1 = I_1' - I_1''$$

,  $I_2 = I_2'' - I_2'$ ,  $I = I' + I''$

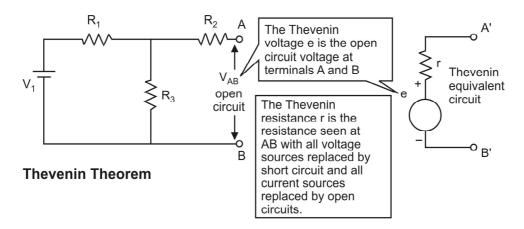

#### THEVENIN THEOREM

Fig. 1.34

It provides a mathematical technique for replacing a given network, as viewed from two output terminals, by a single voltage source with a series resistance. It makes the solution of complicated networks (particularly, electronic networks) quite quick and easy. The application of this extremely useful theorem will be explained with the help of the following simple example.

Fig. 1.35

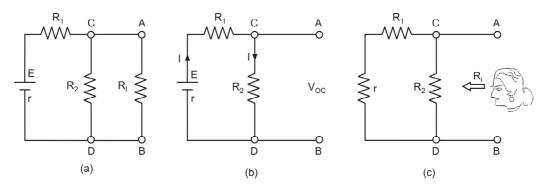

Suppose, it is required to find current flowing through load resistance  $R_L$ , as shown in Fig. 1.35 (a). We will proceed as under :

- 1. Remove  $R_L$  from the circuit terminals A and B and redraw the circuit as shown in Fig. 1.35(b). Obviously, the terminals have become open-circuited.

- 2. Calculate the open-circuit voltage  $V_{oc}$  which appears across terminals A and B when they are open i.e. when  $R_L$  is removed.

As seen,  $V_{OC} = \text{drop across } R_2 = IR_2 \text{ where I is the circuit current when A and B are open.}$

$$I = \frac{E}{R_1 + R_2 + r} \quad \therefore \quad V_{oc} = IR_2 = \frac{ER_2}{R_1 + R_2 + r} \quad [r \text{ is the terminal resitance or battery}]$$

It is also called 'The venin voltage '  $\rm V_{\rm th}.$

3. Now, imaging the battery to be removed from the circuit, leaving its internal resistance r behind and redraw the circuit, as shown in Fig. 1.35 (c). When viewed inwards from terminals A and B, the circuit consists of two parallel paths: one containing  $R_2$  and the other containing  $R_1 + r$ . The equivalent resistance of the network, as viewed from these terminals is given as

$$R = R_2 \| (R_1 + r) = \frac{R_2 (R_1 + r)}{R_2 + (R_1 + r)}$$

This resistance is also called,\* Thevenin resistance  $R_{sh}$  (though, it is also sometimes written as  $R_{sh}$  or  $R_{o}$ ).

Consequently, as viewed from terminals A and B, the whole network (excluding  $R_1$ ) can be reduced to a single source (called Thevenin's source) whose e.m.f. equals  $V_{\infty}$  (or  $V_{\text{sh}}$ ) and whose internal resistance equals  $R_{\text{sh}}$  (or  $R_i$ ) as shown in Fig. 1.36.

Fig. 1.36

4.  $R_L$  is now connected back across terminals A and B from where it was temporarily removed earlier. Current flowing through RL is given by

$$I = \frac{V_{th}}{R_{th} + R_{I}}$$

It is clear from above that any network of resistors and voltage sources (and current sources as well) when viewed from any points A and B in the network, can be replaced by a single voltage source and a single resistance\*\* in series with the voltage source.

After this replacement of the network by a single voltage source with a series resistance has been accomplished, it is easy to find current in any load resistance joined across terminals A and B. This theorem is valid even for those linear networks which have a nonlinear load.

Hence, Thevenin's theorem, as applied to d.c. circuits, may be stated as under:

The current flowing through a load resitance  $R_L$  connected across any two terminals A and B of a linear, avtive bilateral network is given by  $V_{oc} || (R_i + R_L)$  where  $V_{oc}$  is the open-circuit voltage (i.e. voltage across the two terminals when  $R_L$  is removed) and  $R_i$  is the internal resistance of the network as viewed back into the open-circuited network from terminals A and B with all voltage source replaced by their internal resistance (if any) and current sources by infinite resistance.

#### How to Thevenize a Given Circuit

- 1. Temporarily remove the resistance (called load resistance R<sub>1</sub>) whose current is required.

- 2. Find the open-circuit voltage  $V_{oc}$  which appears across the two terminals from where resistance has been removed. It is also called Thevenin voltage  $V_{m}$ .

- 3. Compute the resistance of the whose network as looked into from these two terminals after all voltage sources have been removed leaving behind their internal resistances (if any) and current sources have been replaced by open-circuit i.e. infinite resisance. It is also called Thevenin resistance R<sub>th</sub> or T<sub>t</sub>.

- 4. Replace the entire network by a single Thevenin source, whose voltage is V<sub>th</sub> or V<sub>oc</sub> and whose internal resistance is R<sub>th</sub> or R<sub>t</sub>.

- 5. Connect R<sub>L</sub> back to its terminals from where it was previously removed.

- 6. Finally, calculate the current flowing through R<sub>L</sub> by using the equation,

$$I = V_{th}/(R_{th} + R_L)$$

or  $I = V_{oc}/(R_i + R_L)$

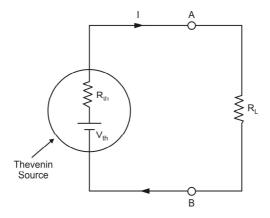

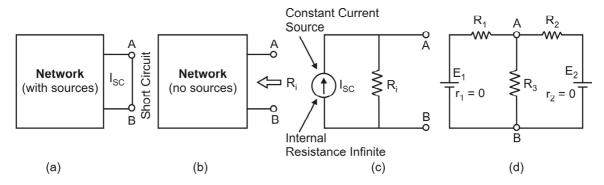

#### NORTON'S THEOREM

This theorem is an alternative to the Thevenin's theorem. In fact, it is the dual of Thevenin's theorem. Whereas Thevenin's theorem reduces a two-terminal active network of linear resistances and generators to an equivalent constant-voltage source and series resistance, Norton's theorem replaces the network by an equivalent constant-current source and a parallel resistance.

This theorem may be stated as follows:

i. Any two-terminal active network containing voltage sources and resistance when viewed from its output terminals, is equivalent to a constant-current source and a parallel resistance. The constant current is equal to the current which would flow in tha short-circuit placed acrossthe terminals and parallel resistance is the resistance of the network when viewed from these open-circuited terminals after all voltage and current sources have been removed and replaced by their internal resistances.

Fig. 1.37

#### Exaplanation

As seen from Fig. 1.37(a), a short is placed across the terminals A and B of the network with all its energy sources present. The short-circuit current  $I_{sc}$  gives the value of constant-current source.

For finding  $R_{,}$ , all sources have been removed as shown in Fig. 1.37(b). The resistance of the network when looked into from terminals A and B gives  $R_{,}$ .

The Norton's equivalent circuit is shown in Fig. 1.37(c). It consists of an ideal constant-current source of infinite internal resistance having a resistance of R, connected in parallel with it.

ii. Another useful generalized form of this theorem is as follows:

The voltage between any two points in a network is equal to  $I_{sc}$ .  $R_i$  where  $I_{sc}$  is the short-circuit current between the two points and  $R_i$  is the resistance of the network as viewed from these points will all voltage sources being replaced by their internal resistances (if any) and current sources replaced by open-circuits.

Suppose, it is required to findthe voltage across resistance  $R_3$  and hence current through it [Fig. 1.37(d)]. If short-circuit is placed between A and B, then current in it due to battery of e.m.f.  $E_1$  is  $E_1/R_1$  and due to the other battery is  $E_2/R_2$ .

$$: \qquad \qquad I_{SC} = \frac{E_1}{R_1} + \frac{E_2}{R_2} = E_1G_1 + E_2G_2$$

where G<sub>1</sub> and G<sub>2</sub> are branch conductances.

Now, the internal resistnace of the network as viewed from A and B simply consists of three resistances  $R_1$ ,  $R_2$  and  $R_3$  connected in parallel between A and B. Please note that here load resistance  $R_3$  has not been removed. In the first method given above, it has to be removed.

$$\therefore \frac{1}{R_i} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} = G_1 + G_2 + G_3$$

$$\therefore \qquad \qquad R_i = \frac{1}{G_1 + G_2 + G_3} \quad \therefore \quad V_{AB} = I_{SC}. \\ R_i = \frac{E_1 G_1 + E_2 G_2}{G_1 + G_2 + G_3}$$

Current through  $R_2$  is  $I_3 = V_{AB}/R_3$ .

Solved example No. 2.96 illustrates this approach.

#### **How To Nortonize a Given Circuit?**

This procedure is based on the first statement of the theorem given above.

- 1. Remove the resistance (if any) across the two given terminals and put a short-circuit across them.

- 2. Compute the short-circuit current I<sub>sc</sub>.

- 3. Remove all voltage sources but retain their internal resisances, if any. Similarly, remove all current sources and replace them by open-circuits i.e. by infinite resistance.

- 4. Next, find the resistance  $R_1$  (also called  $R_N$ ) of the network as looked into from the given terminals. It is exactly the same as  $R_1$ .

- exactly the same as R<sub>th</sub>.

5. The current source (I<sub>SC</sub>) joined in parallel across R<sub>i</sub> between the two terminals gives Norton's equivalent circuit.

#### **Maximum Power Transfer Theorem**

Although applicable to all branches of electrical engineering, this theorem is particularly useful for analysing communication networks. The overall efficiency of a network supplying maximum power to any branch is 50 per cent. For this reason, the application of this theorem to power transmission and distribution networks is limited because, in their case, the goal is high efficiency and not maximum power transfer.

However, in the case of electronic and communication networks, very often, the goal is either to receive or transmit maximum power (through at reduced efficiency) specially when power involved is only a few milliwatts or microwatts. Frequently, the problem of maximum power transfer is of crucial significance in the operation of transmission lines and antennas.

Fig. 1.38

As applied to d.c. networks, this theorem may be stated as follows:

A resistive load will abstract maximum power from a network when the load resistance is equal to the resistance of the network as viewed from the output terminals, with all energy source removed leaving behind their internal resistances.

In Fig. 1.38, a load resistance of  $R_L$  is connected across the terminals A and B of a network which consits of a generator of e.m.f. E and internal resistance  $R_g$  and a serias resistance R which, in fact, represents the lumped resistance of the connecting wires. Let  $R_g = R_g + R =$ internal resistance of the network as viewed from a and B

According to this theorem,  $R_L$  will abstract maximum power from the network when  $R_L = R_L$ .

**Proof.** Circuit current

$$I = \frac{E}{R_1 + R_i}$$

Power consumed by the load is

$$P_{L} = I^{2}R_{L} = \frac{E^{2}R_{L}}{(R_{L} + R_{i})^{2}}$$

For

$$P_L$$

to be maximum,  $\frac{dP_L}{dR_L} = 0$ .

Differentiating Eq. (i) above, we have

$$\begin{split} \frac{dP_L}{dR_L} &= E^2 \Bigg[ \frac{1}{(R_L + R_i)^2} + R_L \Bigg( \frac{-2}{(R_L + R_i)^3} \Bigg) \Bigg] = E^2 \Bigg[ \frac{1}{(R_L + R_i)^2} - \frac{2R_L}{(R_L + R_i)^3} \Bigg] \\ 0 &= E^2 \Bigg[ \frac{1}{(R_L + R_i)^2} - \frac{2R_L}{(R_L + R_i)^3} \Bigg] \text{ or } 2R_L = R_L + R_i \text{ or } R_L = R_i \end{split}$$

It is worth noting that under these conditins, the voltage across the load is hold the open-circuit voltage at the terminals A and B.

$$\therefore \qquad \text{Max power is } P_{\text{Lmax}} = \frac{E^2 R_L}{4R_L^2} = \frac{E^2}{4R_L} = \frac{E^2}{4R_i}$$

Let us consider an a.c. source of internal impedance  $(R_1 + j X_1)$  supplying power to a load impedance  $(R_L + j X_L)$ . It can be proved that maximum powr transfer will take place when the modules of the load impedance is equal to the modulus of the source impedance i.e.  $|Z_1| = |Z_2|$ .

Where there is a completely free choice about the load, the maximum power transfer is obtained when load impedance is the complex conjugate of the source impedance. For example, if source impedance is  $(R_1 + jX_1)$ , then maximum transfer power occurs, when load impedance is  $(R_1 - jX_1)$ . It can be shown that under this condition, the load power is =  $E_2/4R_1$ .

## **UNIT - 2**

## **CHAPTER - 2 Alternating Currents**

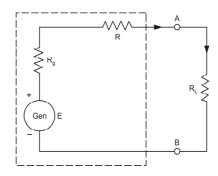

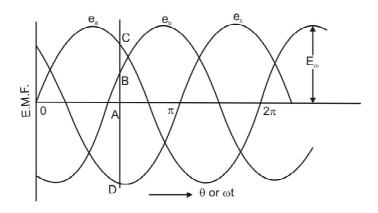

#### ALTERNATING VOLTAGE AND CURRENT

If the polarity of voltage change with time, it is know as an alternating voltage. The current that such a voltage causes to flow repeatedly changes its direction and is called alternating current.

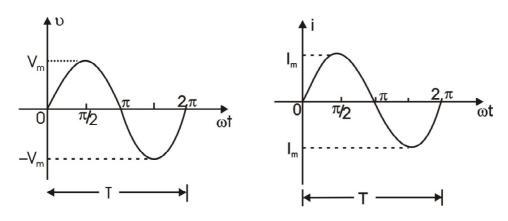

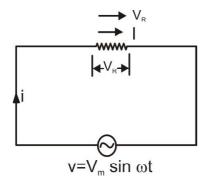

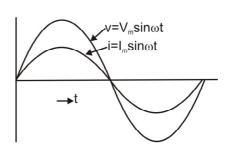

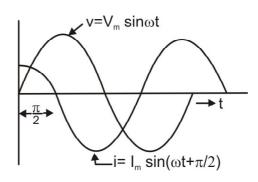

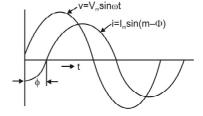

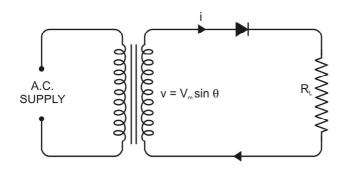

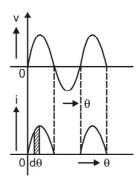

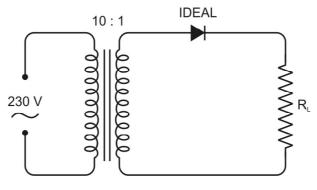

i. **Sinusoidal alternating voltage:** The most commonly encountered type of alternating voltage varies sinusoidally with time. A sinusoidal alternating voltage can be produced by rotating a coil with constant angular ω velocity (sayrad/sec) in a uniform magnetic field. The sinusoidal alternating voltage can be expressed by the equation:

$v = V_m \sin ωt$

where  $\omega = \text{value of alternating voltage at time t (called}$

instantaneous value)

V = maximum value of alternating voltage

$\omega$  = angular velocity of the coil

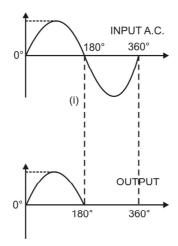

Fig. 12.1(i) shows the waveform of sinusoidal alternating voltage. Note that voltage varies from zero to a positive peak  $(+V_m)$ , then back via zero to a negative peak (-Vm) and so on. In time period T, the wave completes one cycle.

Fig. 2.1

ii. Sinusoidal Alternating current: A sinusoidal alternating voltage applied in a circuit results in a sinusoidal alternating current can be represented in the same way as voltage i.e.,

$i = I_m \sin \omega t$

where i = value of alternating current at time t (called instantaneous

value)

$I_{m}$  = maximum value of alternating current.

Fig. 2.1(ii) shows the waveform of sinusoidal alternating current. Note that sinusoidal voltage or current not only changes direction at regular intervals but the magnitude is also changing continuously.

Note: Alternating voltage and current mean sinusoidal alternating voltage and current unless stated otherwise.

Therefore, we shall omit the word 'sinusoidal' in our further discussion.

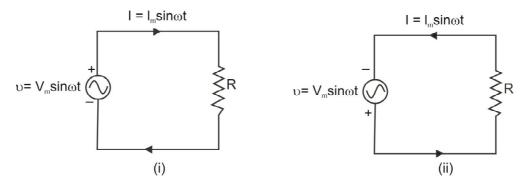

#### FLOW OF ALTERNATING CURRENT

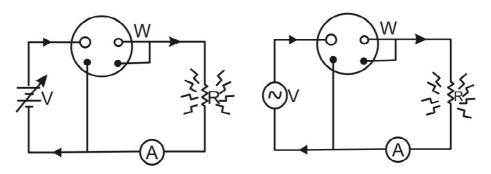

Fig. 2.2 (i) shows an alternating voltage source connected to a resistor R. In Fig. 2.2(i), the upper terminal of alternating voltage source is positive and the lower terminal negative so that current flows in the circuit as shown. After time equal to T/2 (where T is the time period of alternating voltage), the polarities of the voltage source are reversed [See Fig. 2.2(ii)] so that current now flows in the opposite direction. This is called alternating current because the current flows in alternate directions in the circuit.

Fig. 2.2

Note that alternating current has the same frequency ( $\omega = 2\mu f$ ) as the alternating voltage that produces it. Therefore, when an alternating voltage is applied in a circuit, the resulting current has the same frequency as that of applied voltage.

#### IMPORTANT A.C. TERMINOLOGY

The important a.c. terminology is defined below:

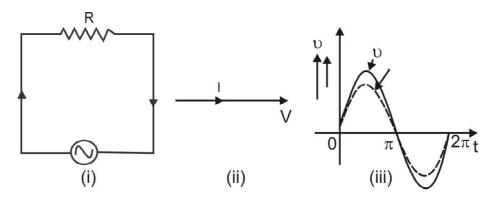

- i. **Waveform:** The shape of the curve obtained by plotting the instantaneous values of voltage or current as ordinate against time as abcissa is called its waveform or waveshape. Fig.11.3 shows the waveform of an alternating voltage varying sinusoidally.

- ii. Instantaneous value: The value of an alternating quantity at any instant is called its instantaneous value. The instantaneous values of alternating voltage and current are represented by υ and i respectively. As example, the instantaneous values of voltage (See Fig. 2.3) at 0°, 90° and 270° are 0, + V<sub>m</sub> and -V<sub>m</sub> respectively.

Fig. 2.3

- iii. **Cycle**: One complete set of positive and negative values of an alternating quantity is known as a cycle Fig. 2.3 shows one cycle of an alternating voltage.

- A cycle can also be defined in terms of angular measure. One cycle corresponds to 360° electrical or  $2\pi$  radians. The voltage or current generated in a conductor will span 360° electrical (or complete one cycle) when the conductor moves past a north and south pole.

- iv. **Alternation.** one-half cycle of an alternating quantity is called an alternation. An alternation spans 180° electrical. Thus in Fig. 2.3, the positive or negative half of alternating voltage is the alternation.

- v. **Time period.** The time taken in seconds to complete one cycle of an alternating quantity is called its time period. It is generally represented by T.

- vi. **Frequency.** The number of cycles that occur in one second is called the frequency (f) of the alternating quantity. It is measured in cycles/sec (C/s) or Hertz (Hz). One Hertz is equal to 1C/s.

- The frequency of power system is low; the most common being 50 C/s or 50 hz. It means that alternating voltage or current completes 50 cycles in one second. The 50 Hz frequency is the most popular because it gives the best results when used for operating both lights and machinery.

- vii. **Amplitude.** The maximum value (positive or negative) attained by an alternating quantity is called its amplitude or peak value. The amplitude of an alternating voltage or current is designed by  $V_m(or E_m)or I_m$ .

#### **IMPORTANT RELATIONS**

Having become familiar with a.c. terminology, we shall now establish some important relations.

i. **Time period and frequency**: Consider an attenuating quantity having a frequency of f C/s and time period T second.

Time taken to complete f cycles = 1 second

Time taken to compete 1 cycle = 1/f second

But the time taken to complete one cycle is the time period T (by definition).

$$T = \frac{1}{f} \text{ or } f = \frac{1}{T}$$

ii. **Angular velocity and frequency :** Suppose the coil is rotating with an angular velocity of  $\omega$  rad/sec in a uniform magnetic field. In one revolution of the coil, the angle turned is  $2\pi$  radians and the voltage wave completes 1 cycle. The time taken to complete one cycle is the time period T of the alternating voltage.

$$\therefore \qquad \text{Angular velocity, } \omega = \frac{\textit{Angle turned}}{\textit{Time taken}} = \frac{2\pi}{\textit{T}}$$

or

$$\omega = 2\pi \textit{f} \qquad (\because f = 1/T)$$

iii. **Frequency and speed.** Consider a coil rotating at a speed of N r.p.m. in the field of p poles. As the coil moves past a north and south pole, one complete cycle is generated. Obviously, in one revolution of the coil, P/2 cycles will be generated.

Now, Frequency, f = No of cycles/sec

= (No. of cycles/revolution) × (No. of revolutions/sec)

$$= \left(\frac{P}{2}\right) \times \left(\frac{N}{60}\right) = \frac{PN}{120}$$

$$f = \frac{NP}{120}$$

For example, an a.c. generator having 10 poles and running at 600 r.p.m. will generate alternating voltage whose frequency is:

$$f = \frac{NP}{120} = \frac{10 \times 600}{120} = 50Hz$$

.

#### **GENERATION OF ALTERNATING VOLTAGE AND CURRENTS**

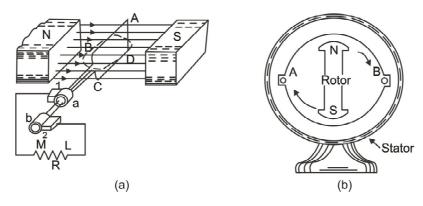

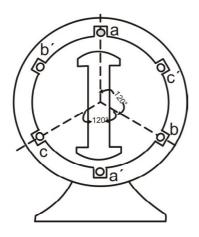

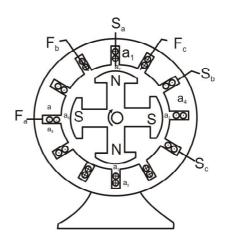

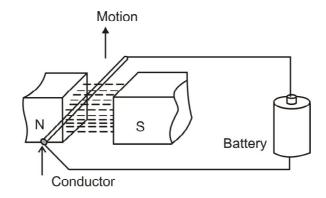

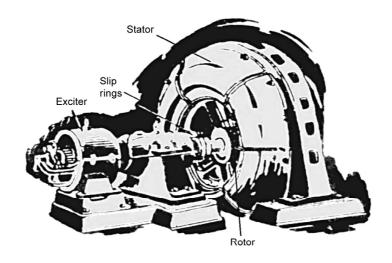

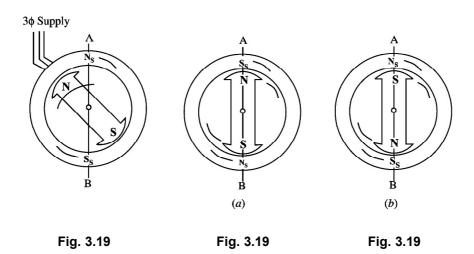

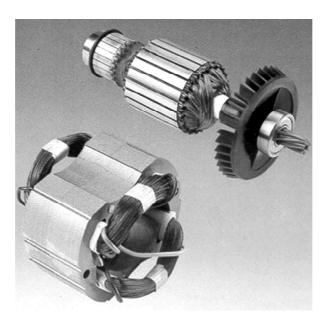

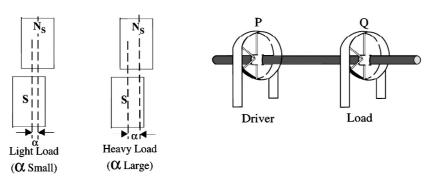

Alternating voltage may be generated by rotating a coil in a magnetic field, as shown in Fig.2.4(a) or by rotating a magnetic field within a stationary coil, as shown in Fig.2.4(b).

Fig. 2.4

The value of the voltage generated depends, in each case, upon the number of turns in the coil, strength of the field and the speed at which the coil or magnetic field rotates. Alternating voltage may be generated in either of the two ways shown above, but rotating-field method is the one which is mostly used in practice.

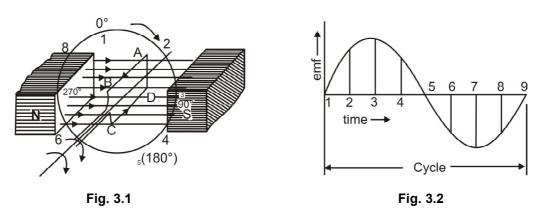

#### **Equations of the Alternating Voltages and currents**

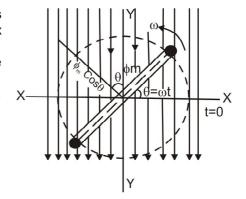

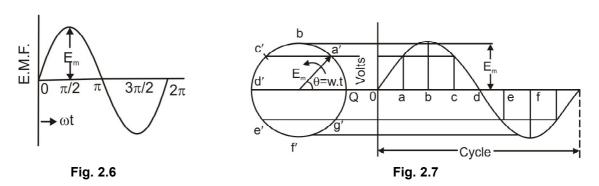

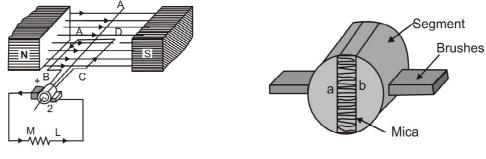

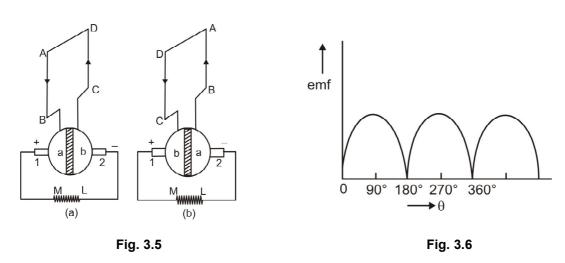

Consider a rectangular coil, having N turns and rotating in a uniform magnetic field, with an angular velocity of  $\omega$  radian/second, as shown in Fig.2.5. Let time be measured from the X-axis. Maximum flux  $\Phi_m$  is linked with the coil, when its plane coincides with the X-axis. In time t seconds, this coil rotates through an angle  $\theta = \omega t$ .

In this deflected position, the component of the flux which is perpendicular to the plane of the coil, is  $\Phi = \Phi_m \cos \omega t$ . Hence, flux linkages of the coil at any time are  $N\Phi = N\Phi_m \cos \omega t$ .

According to Faraday's Laws of Electromagnetic Induction, the e.m.f. induced in the coil if given by the rate of change of flux-linkages of the coil. Hence, the value of the induced e.m.f. at this instant (i.e. when  $\theta$  =  $\omega t)$  or the instantaneous value of the induced e.m.f. is

$$e = -\frac{d}{dt}(N\Phi) \text{ volt} = -N \cdot \frac{d}{dt}(\Phi_m \cos \omega t) \text{ volt} = -N\Phi_m \omega (-\sin \omega t) \text{ volt}$$

$$= \omega N\Phi_m \sin \omega t \text{ volt} = \omega N\Phi_m \sin \theta \text{ volt}$$

...(i)

When the coil has turned through 90° i.e. when  $\theta$  = 90°, then sin  $\theta$  = 1, hence e has maximum value, says  $E_m$ . Therefore, from Eq.(i) we get

Fig. 2.5

$$E_m = \omega n \Phi_m = \omega N B_m A = 2\pi f N B_m A$$

volt ...(ii)

where

$B_{m}$  = maximum flux density in Wb/m<sup>2</sup>; A = area of the coil in m<sup>2</sup>

f = frequency of rotation of the coil in rev/second

Substituting this value of  $E_m$  in Eq. (i), we get  $e = E_m \sin \theta = E_m \sin \omega t$ Similarly, the equation of induced alternating current is  $i = I_m \sin \omega t$ ...(iii)

...(iv) provided the coil circuit has been closed through a resistive load.

Since  $\omega = 2\pi f$ , where if is the frequency of rotation of the coil, the above equations if the voltage and current can be written as

e =

$$E_m \sin 2\pi f t = E_m \sin \left(\frac{2\pi}{T}\right) t$$

and  $i = I_m \sin 2\pi f t = I_m \sin \left(\frac{2\pi}{T}\right) t$

where

T = time-period of the alternating voltage or current = 1/f

It is seen that the induced e.m.f. varies as sine function of the time angle ωt and when e.m.f. is plotted against time, a curve similar to the one shown in Fig.2.6 is obtained. This curve is known as sine curve and the e.m.f. which varies in this manner is known as sinusoidal e.m.f. Such a sine curve can be conveniently drawn, as shown in Fig.2.7. A vector, equal in length to  $E_m$  is drawn. It rotates in the counter-clockwise direction with a velocity of ω radian/second, making one revolution while the generated e.m.f. makes two loops or one cycle. The projection of this vector on Y-axis gives the instantaneous value e of the induced e.m.f. i.e.  $E_m \sin \omega t$ .

To construct curve, lay off along X-axis equal angular distance oa, ab, bc, cd etc. corresponding to suitable angular displacement of the rotating vector. Now, erect coordinates at the points a, b, c and d etc. (Fig. 2.7) and then project the free ends of the vector E, at the corresponding position a', b', c', etc to meet these ordinates. Next draw a curve passing through these intersecting points. The curve so obtained is the graphic representation of equation (iii) above.

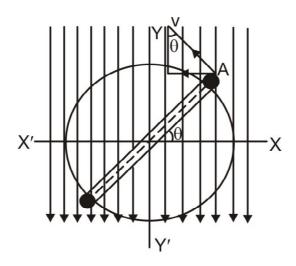

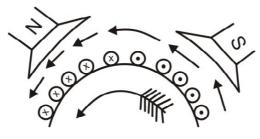

#### Alternate Method for the Equations of Alternating Voltages and Currents

In Fig.2.8 is shown a rectangular coil AC having N turns and rotating in a magnetic field of flux density B Wb/m<sup>2</sup>. Let the length of each of its sides A and C be/meters and their peripheral velocity v metre/second. Let angle be measured from the horizontal position i.e. from the X-axis. When in horizontal position, the two sides A and C move parallel to the lines of the magnetic flux. Hence, no flux is cut and so no e.m.f. is generated in the coil.

Fig. 2.8

When the coil has turned through angle  $\theta$ , its velocity can be resolved into two mutually perpendicular components (i)  $v\cos\theta$  component-parallel to the direction of the magnetic flux and (ii)  $v\sin\theta$  component-perpendicular to the direction of the magnetic flux. The e.m.f. is generated due entirely to the perpendicular component i.e.  $v\sin\theta$ .

Hence, the e.m.f. generated in one side of the coil which contains N conductors, is given by,  $e = N \times Bl \ v \sin \theta$ .

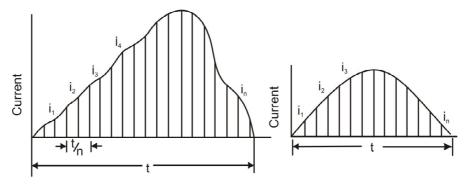

#### Root-Mean-Square (R.M.S) Value

The r.m.s value of an alternating current is given by that steady (d.c.) current which when flowing through a given circuit for a given time produces the same heat as produced by the alternating current when flowing through the same circuit for the same time.

It is also known as the effective or virtual value of the alternating current, the former term being used more extensively. For computing the r.m.s. value of symmetrical sinusoidal alternating currents, either mid-ordinate method or analytical method may be used, although for symmetrical but non-sinusoidal waves, the mid-ordinate method would be found more convenient.

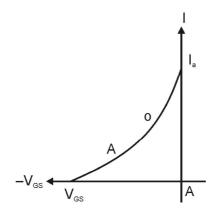

Fig. 2.9